🚀 Ever heard of Self-Heating in FinFETs?

As devices shrink, FinFETs squeeze more power into tighter spaces—🔥 but that comes with heat!

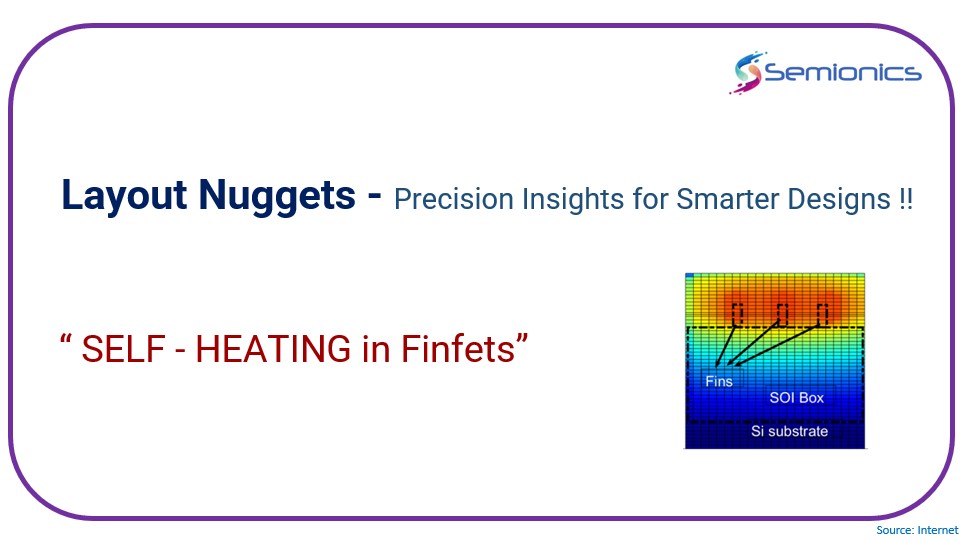

Self-heating is the localized temperature rise inside a transistor, caused by dense fins and insulating materials that trap heat.

🔎 Why should you care?

Analog Layouts → Impacts matching & linearity (a big no for precision).

Digital Layouts → Slows timing paths & reduces long-term reliability.

💡 Layout Engineers’ Playbook:

✔ Optimize fin density

✔ Space thermally

✔ Use guard rings / dummy heat sinks

(Remember—layout isn’t just geometry, it’s thermal engineering!)

💡 Circuit Designers’ Checklist:

✔ Reduce power density

✔ Balance current flow

✔ Apply thermal-aware biasing

That’s your #LayoutNugget 🎯 — keep it cool, keep it reliable.

Happy Learning!

Feel Free to connect with us on all the platforms mentioned below ..!

👉 Register for Free on Semionics-academy !:

https://academy.semionics.com/s/store?redirectToMicroFE=true

👉Follow our Linkedin Page :

https://www.linkedin.com/company/semionics-academy/?viewAsMember=true

👉Subscribe and share our You tube videos and channel :

https://www.youtube.com/@semionics5352

👉Subscribe and share our You tube videos and channel :

https://www.youtube.com/@semionics5352

👉WhatsApp , Semionics-Global Connect !

https://chat.whatsapp.com/FRDdfKi20cA5sBgun2iNeL

Mobile/WhatsApp: +91- 8904212868 Email: enquiry@semionics.com , semionics@gmail.com

More to come…

#vlsi #analoglayout #physicaldesign #semiconductors #semionics #layout #chipdesign #icdesign #eda #learningseries #LayoutEngineers #physicalverification #FinFET #SelfHeating #VLSIDesign #AnalogDesign #DigitalDesign #LayoutTips #ThermalEngineering #ICDesign