In an industry long dominated by proprietary architectures, RISC-V has emerged as a powerful symbol of openness, collaboration, and innovation. With its open-source instruction set architecture (ISA), RISC-V empowers startups, universities, and even hobbyists to design and customize processors without restrictive licensing costs. However, with this freedom comes complexity. The real challenge begins not in coding RTL or synthesizing logic, but in physical implementation and layout design — where ideas meet the harsh realities of silicon.

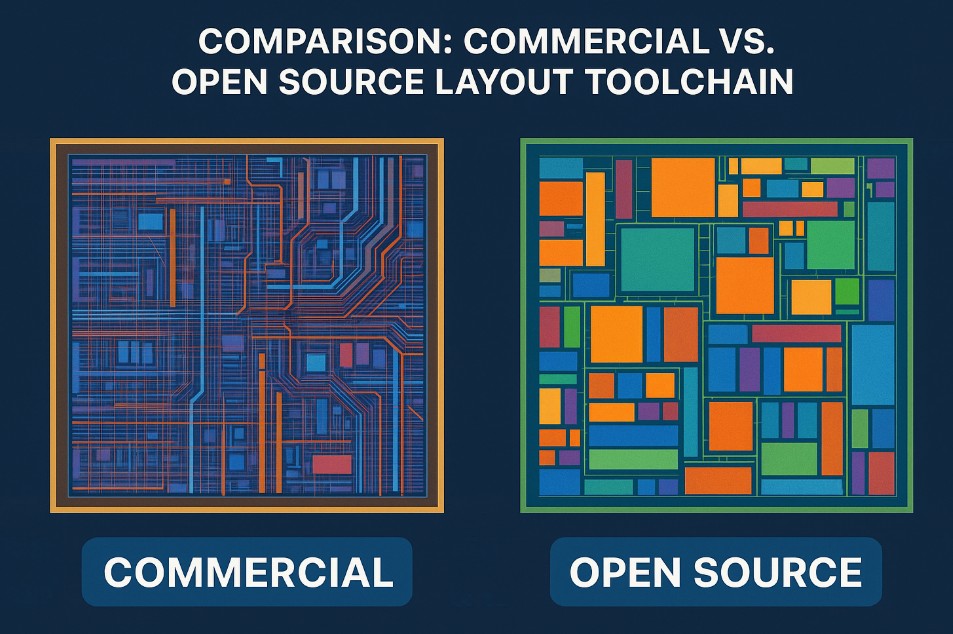

The open-source silicon movement — led by platforms like OpenROAD, SkyWater 130nm, and Google’s OpenMPW initiative — has made chip fabrication more accessible than ever before. Yet, layout design for open-source chips introduces new engineering hurdles. Unlike commercial ASIC flows with highly optimized process design kits (PDKs) and EDA toolchains, open-source environments face:

These gaps demand that layout engineers adopt hybrid design methodologies — combining open tools with custom verification scripts and manual optimization techniques.

“Freedom to design comes with the responsibility to understand what the tools can’t do for you.”

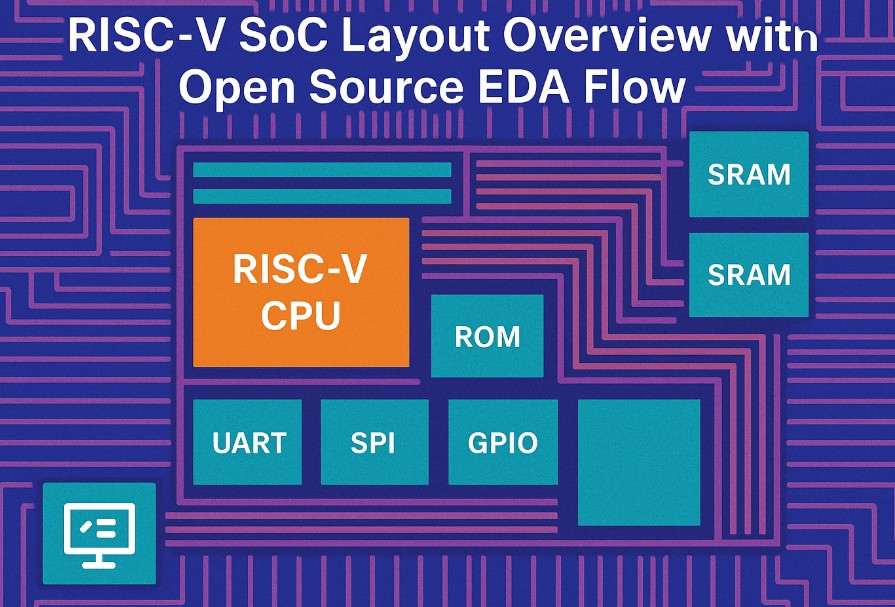

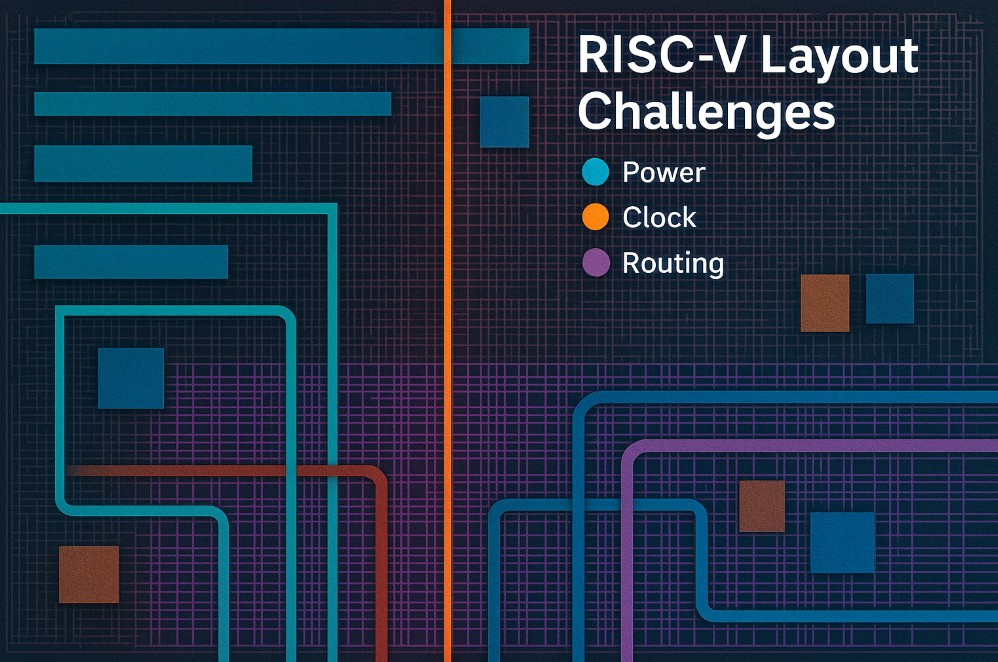

Designing a RISC-V processor core involves the integration of multiple domains — logic, memory, analog, and IO — all on a single die. Each domain introduces unique layout challenges that influence performance, timing closure, and yield.

Here are some of the most common:

Despite these limitations, engineers are finding creative ways to build high-quality, manufacturable open-source chips. Some proven strategies include:

“Open-source design thrives when engineers share, not just code — but experience.”

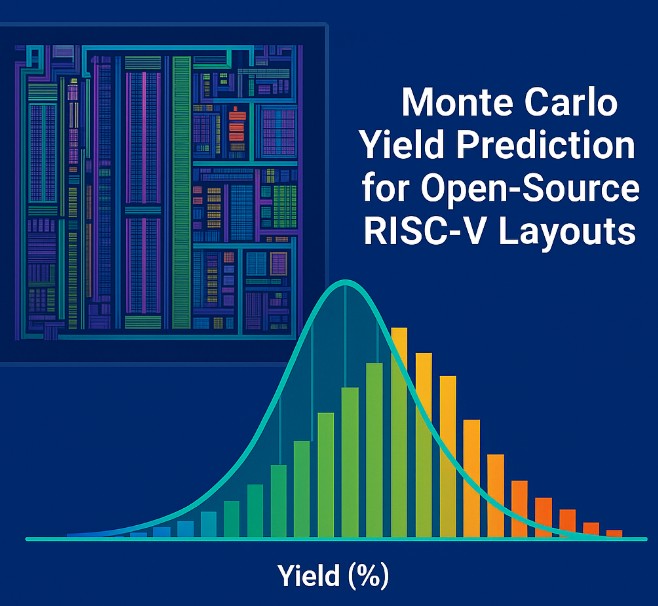

In open PDK environments, corner analysis and Monte Carlo simulations are often less robust compared to proprietary toolchains. This makes layout-aware verification even more critical. Engineers must perform layout-dependent simulations and parameter sweeps to model potential yield losses due to process variability, IR drop, and crosstalk. Without full access to foundry process data, empirical modeling and community-tested heuristics play a crucial role in yield optimization.

As the RISC-V ecosystem matures, the collaboration between academia, startups, and open hardware communities is accelerating. Future flows will likely integrate AI-assisted floorplanning, machine-learning-based timing prediction, and automated yield optimization into open EDA platforms.

Semionics is at the forefront of this transformation — inspiring, educating, and enabling engineers

“When knowledge is shared, silicon innovation becomes limitless.”

📞 Connect with Semionics

The images and content used in this blog are generated, created, or referenced from Google Images and other educational sources. They are intended purely for educational and guidance purposes, with no intention of monetization. All credits belong to the respective owners. Semionics holds no responsibility for third-party content and encourages readers to verify before use.